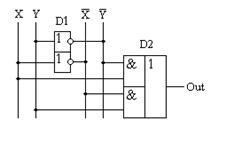

В съответствие с принципите на схемите за тяхното осъществяване printsipialnoy произволна маса истина обсъдени в предишните раздели, ние се получи схема на модул разширител 2. Формирането на тази верига не се различава от предишните примери, обсъдени по-рано. Както и преди избрани линии, съдържащи единица в изходния сигнал. Те се реализира с елементи "2i". Нула потенциали на входните сигнали в тези редове се превръщат в отделни използват инвертори. Комбинирането на изходите на логически елементи в логиката елемент е направен "2или". Получената електрическата схема на разширител по модул 2 е показана на Фигура 15.1.

Фигура 15.1 - Схематична диаграма, която изпълнява истина маса разширител по модул 2

Ехидна модул 2 (за два входа схема му е идентичен с верига изключителен "ИЛИ") е изобразена на диаграми верига, както е показано на фигура 15.2.

Фигура 15.2 - Условни графични схеми за отбелязване, да извършват "изключителна ИЛИ" логика функция

Modulo-2 разширител извършва допълнение без оглед на прехвърляне между битовете. Пълният двоичен ехидна, че е необходимо да се помисли, следователно, необходими елементи, дават възможност за развитието на транспорта в следващия бит. Таблицата с истината на устройството, наречено половин усойница е показано в Таблица 15.2.

Имайте предвид, че сигналите в следната таблица истина подредени по реда, приет за веригите, които са в съответствие с факта, че сигналът се разпространява от ляво на дясно. В резултат на прехвърлянето, която има двоичен голяма тежест в сравнение с интегрируеми записани бита надясно. В математиката, получи още един ред от цифри на номера. В MSB на най-лявата хартията се записва, както и най-маловажният бит е написано правилно. Това може да доведе до объркване. За да предотвратите това, тук е десетичния еквивалент на всеки ред от половин ехидна истина маса (таблица 15.2).

Първият ред на таблицата на истината се получава от аритметични изрази 0 + 0 = 010 (002). Вторият ред се получава от аритметични изрази 0 + 1 = 110 (012). Третият ред се получава от аритметични изрази 1 + 0 = 110 (012). Четвъртият ред се получава от аритметичен израз 1 + 1 = 210 (102).

Таблица 15.2 - масата за половин ехидна истина

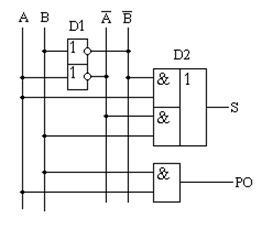

В съответствие с принципите на изграждане на произволна маса истина получаваме схема на полу-ехидна. Схема съответстващ истина маса, съдържаща се в таблица 15.2 е показан на фигура 15.3.

Фигура 15.3 - Схема на цифрово устройство, който реализира таблицата истината на половин ехидна

След половин разширител произведени като отделни чипове и се използват като отделни модули в големи интегрални схеми, обаче ГОСТ предвидени условно графичен наименование половин разширител. Това е показано на Фигура 15.4.

Фигура 15.4 - Условно графична нотация половин разширител

Половин ехидна генерира пренасяне към следващата цифра, но не може да вземе предвид прехвърлянето на предишното освобождаване от отговорност, и затова той се нарича половин усойница. В резултат на този половин разширител може да се използва като отделно устройство. От практически интерес е пълен усойница.

Истината маса, пълна с едноцифрен двоичен усойница (таблица 15.3), както и таблицата за половин ехидна истина може да бъде получена от правилата на аритметиката сумиране на двоични числа. Определянето на входовете и изходите на пълен ехидна използва следното правило: като суровини, използвани единично-битов двоични числа А и Б; сумата от - една цифра двоично число S; прехвърляне, определен от буква Р; входове за прехвърляне на символи с помощта на комбинация от букви PI (I - съкращение от английската дума вход, вход); да се посочи прехвърлянето изход чрез комбинация от букви PO (O - съкращение от дума изхода на английски, добив).

Таблица 15.3 - истината маса, пълна бинарна

Сега, точно както и в предишните случаи, в съответствие с правилата на строителството понятие маса произволна истина получаваме веригата пълна бинарна един-битов усойница. Схема съответстващ истина маса съдържа в таблица 14.3 е показан на фигура 15.5. Тази схема се конструира при използване PDNF.

Фигура 15.5 - Схема с която се прилага таблицата истината на двоичен един-битов пълен ехидна

Circuit пълен един-битов ехидна могат да бъдат сведени до минимум. Това е достатъчно, за да погледнете в последните две от своята истина ред в таблицата. Можем да видим, че пренасянето на сигнала, че не зависи от настоящето на входния сигнал Б. Ето защо, на входа не може да започне на входа схема "И".

В резултат, вместо двете описано разсъждения долните елементи "3I" може да се използват два входа елемент "2i". Същата ситуация се случва, ако се вземат предвид линиите 6 и 8. В този случай, на входа е излишно А. Това означава, че в този случай е възможно да се управлява един два входа и врата "2i".

Вход PI е излишно по отношение описващи линия 4 и 8. В резултат на тази процедура, схема на пренасянето на следващата цифра суматора е опростено и има формата, е показана на Фигура 15.6.

Фигура 15.6 - Намалена схема, която се прилага таблицата истината от една-битов двоичен пълен ехидна

Пример за един-битов двоичен усойница може да служи като вторичен интеграция чип K155IM1. Свързани графичен символ двоичен един-битов пълен разширител е показано на Фигура 15.7.

Фигура 15.7 - още графично представяне на бинарния един-малко пълно суматора

Въпреки това, за извършване на изчисления в цифровата обработка на сигнала вериги недостатъчната точност един-битов разширители. Те използват 16- или дори 40-битов двоичен усойница.

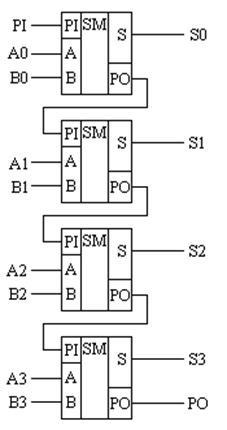

За да се получи мулти-битов ехидна на над един-битов ехидна, това е достатъчно, за да се свържете на входовете и изходите на съответните бита трансферите. Схема на четири цифри суматора осъществява в четири едно малко разширител, показан на фигура 15.8.

Фигура 15.8 - Схематична диаграма на четири битова двоична суматора

В диаграмата на двоични цифри сумират тегло на номера А и В е пряко картирани в заглавието съединение. Например, А0 верига предава нула цифра от А, В2 верига предава втората цифра от Б. PI входни и изходни имена трансфер PO се променят.

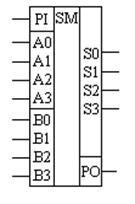

Четири-битова двоична пълен разширител е показано в Схеми използват условно графично нотация е показано на фигура 15.9. Имайте предвид, че тази бройна дума двоични входове комбинират в едно поле. По същия начин, комбинирани входове двоични думи Б. въвеждане и извеждане пренос сигнали към горните условни графична нотация чипове също подчертани в отделните области. Изобразени по този начин чипа е много по-визуално показва неговата функция.

Фигура 15.9 - Условно пиктограма пълно 4-битова двоична разширител в Схеми

Таблицата на фиг 15.8 схема не е оптимизирана за скорост, служи само за илюстрация на принципа на работа на мулти-битова двоична разширител. Веригите, наети на практика никога не позволяват сериен носене разпространение през всички части от мулти-битов усойница, тъй като намалява скоростта му.

За да се увеличи скоростта на двоичен суматор с помощта на отделен токов кръг на прехвърлянето за всяка битова позиция. истина маса за тази верига се получават лесно от алгоритъм сумиране на двоични числа и след това се прилага най-известните принципи на нашите цифрови устройства от всякакъв маса истина.

Друго, широко използвани в схемите на апарат цифрова обработка на сигнала, двоичен цифров множител. Тези устройства се използват в скалиращите схеми (усилватели или шумозаглушители) или хетеродинни сигнали, и като част от цифрови филтри.

Свързани статии