Анотация: Целта на лекцията въвежда компилативен и интерпретативен представяне логика. Ние считаме, че процесът на контрол симулация описва основните алгоритми на събитие логика симулация.

Вътрешната (машини) схеми модел

След въвеждане на външни описания на контролера в компютър. се превежда във вътрешна представяне на устройство, което се използва директно в процеса на логика симулация. Съществуват две основни форми (модели) вътрешния представяне на контрол - Съставяне и интерпретиране. Когато компилативен модел описание външен контролер като структурен модел (схема) или използвайки функционален програма YARP излъчване в някои език за програмиране (обикновено С или асемблер), които директно изпълнява процеса на моделиране. Когато интерпретативен модел външно описание е преведен на система от свързани таблици, които след това се използват от универсалната програма симулация.

компилация модел

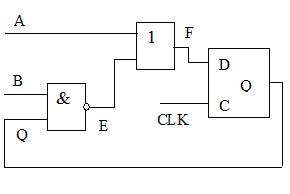

Описанието симулация схема на метод компилация е преведен на поредица от езикови изявления за програмиране или машинни инструкции. Например, синхронни последователни вериги, показани на Фигура 5.1 могат да бъдат превърнати в следната програма долу в Обява "компилация модел."

алгоритъм компилация симулация [39] е показан в Псевдокод обява в "Компилация моделиране". Трябва да се отбележи, че в този случай, първо трябва да се класира на схемата през нивата. Основното предимство на метода на съставяне на симулация е неговата висока скорост. Недостатъците включват факта, че моделът с промени схемата (в процеса на проектиране) всеки път, когато трябва да се компилира отново. Там обикновено се използва чрез (а не събитие задвижване) симулация, в който на всяка итерация стойността на всяка логика елемент преизчислява.

Фиг. 5.1. Схема за компилативен модел

Освен това, за извършване на предварително счупване обратни връзки, необходими за последователни вериги (съответстващи алгоритми, предназначени за тази цел). Но основният проблем на този метод се дава време на изчакване логически елементи. Ето защо, този метод се използва основно при моделиране на комбинаторни и синхронни последователни вериги. В същото време, като правило, тя се проверява само логика, но не и отношението на времето.

интерпретативен модел